ISSN (Print): 2328-3777, ISSN (Online): 2328-3785, ISSN (CD-ROM): 2328-3793

AIJRFANS is a refereed, indexed, peer-reviewed, multidisciplinary and open access journal published by International Association of Scientific Innovation and Research (IASIR), USA (An Association Unifying the Sciences, Engineering, and Applied Research)

# FFT based DTMF detection by using Spartan 3E FPGA

S Nagakishore Bhavanam<sup>1</sup>, Dr. P. Siddaiah<sup>2</sup>, Dr. P. Ramana Reddy<sup>3</sup>

Department of Electronics & Communication Engineering

<sup>1</sup>Research Scholar, University College of Engineering & Technology, JNTU Ananthapuramu, INDIA.

<sup>2</sup>Professor & Dean, University College of Engineering & Technology,

Acharya Nagarjuna University, Guntur, INDIA.

<sup>3</sup>Assoc. Prof., University College of Engineering & Technology, JNTU Ananthapuram, INDIA.

Abstract: DTMF is a method of representing the digits with tones for transmission. Dual Tone Multi Frequency (DTMF) tones are used by all touch tone phones to represent the digits on a touch tone keypad. DTMF technology provides a robust alternative to rotary telephone systems and allows user-input during a phone call. This feature has enabled interactive, automated response systems such as the ones used for routing customer support calls, telephone banking, voicemail, and other similar applications. This paper explains about the FFT based DTMF detection by using Spartan 3e FPGA. FFT based Technique is basically used for detecting the DTMF. Mentor Graphics Modelsim Xilinx Edition (MXE) is used for the Functional Verification and Xilinx ISE is used for Synthesis & simulation respectively. The Xilinx Spartan 3e FPGA Family board is used in this paper.

Keywords: FFT; DTMF; Xilinx ISE; Modelsim; Spartan 3E FPGA

### I. INTRODUCTION

Dual Tone Multiple Frequency (DTMF) signaling is used in telephone dialing, interactive banking systems, digital answer machines. DTMF signaling represents each symbol on a telephone touchtone keypad (0 to 9, \*, #, A-D) using two sinusoidal tones, as shown in Fig. 1. When a key is pressed, a DTMF signal consisting of a row frequency tone plus a column frequency tone is transmitted. Keys A,B,C,D are not on commercial telephone sets, but are used in military and radio signalling applications. The maximum dialling rate is 10 symbols/s in the Bellcore standard [1], [2] and 12.5 symbols/s in the International Telecommunication Union (ITU) Q.24 standard [3].

ITU specifications require that, the valid DTMF signals have their high and low frequency tones within a tolerance of  $\pm 1.5\%$  of an ideal DTMF frequency. If the tolerance of either tone is outside  $\pm 3.5\%$ . Then the signal should be rejected as invalid. ITU specifications place requirements on the duration, and pauses between valid DTMF signals. ITU specifications require 100% detection of valid DTMF signals at 15 dB SNR (Signal to Noise Ratio). Bellcore provides test tapes to measure the performance of a DTMF detector against talk-off, which is false detection of speech signals as DTMF signals.

| 1               | <b>2</b> | 3<br>DEF  | A |

|-----------------|----------|-----------|---|

| <b>4</b><br>вні | <b>5</b> | 6<br>MNO  | В |

| 7<br>PORS       | <b>8</b> | 9<br>wxyz | С |

| *               | Ô        | #         | D |

Fig.1 DTMF Scheme for Touch Tone Dialing (Courtesy from IEEE Transactions on Signal Processing)

### II. PROPOSED ARCHITECTURE DESIGN

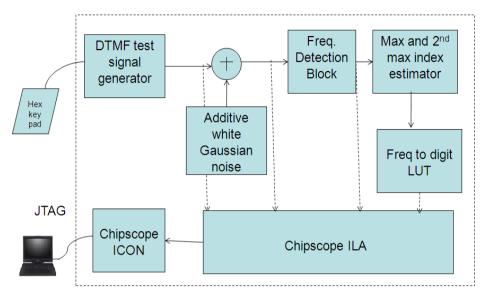

The proposed Architecture can be showed in Fig.2.

Fig.2 DTMF Detection General Module

It consists of the following modules:

- 1. Hex key pad

- 2. DTMF signal generator

- 3. Additive white Gaussian noise

- 4. Frequency Detection block

- 5. Magnitude / index estimator

- 6. Frequency to digit look-up table

### 1. Hex keypad:

The Hex Keypad gives the input to the module. It is an external component. The signal from column is taken as input. Row and display are the output signals.

### 2. DTMF test signal generator:

The DTMF test signal generator block generates that, the carrier frequencies necessary. It consists of two blocks

### 2.1 Frequency word selector:

In this block the carrier waves are generated according to the key pressed 'o'.

### For example:

If key 9 is being press the frequencies that are generated are 852 Hz (Low frequency group) & 1477 Hz (High frequency group). These frequency waves are generated by a DDS core.

### 2.2 DDS Core:

The LogiCORE™ IP DDS (Direct Digital Synthesizer) Compiler core sources sinusoidal waveforms for use in many applications. A DDS consists of a Phase Generator and a SINE/COS Lookup Table. These parts available individually or combined via this core. Direct digital synthesis (DDS) is a method of producing an analog waveform—usually a sine wave by generating a time-varying signal in digital form and then performing a digital-to-analog conversion. Because operations within a DDS device are primarily digital, it can offer fast switching between output frequencies, fine frequency resolution, and operation over a broad spectrum of frequencies. With advances in design and process technology, today's DDS devices are very compact and draw little power.

### 3. Additive white Gaussian Noise:

The tone out, which is the output from tones generator is mixed with noise in this module. The output is named as noise bits. Wideband Gaussian noise comes from the many natural sources, such as the thermal vibrations of atoms in conductors (referred to as thermal noise or Johnson-Nyquist noise), shot noise, black body radiation from the earth and other warm objects, and from celestial sources such as the Sun. The AWGN channel is a good model for many satellite and deep space communication links. It is not a good model for most terrestrial

links because of multipath, terrain blocking, interference, etc. However, for terrestrial path modeling, AWGN is commonly used to simulate background noise of the channel under study, in addition to the multipath, terrain blocking, interference, ground clutter and self interference that modern radio systems encounter in terrestrial operation.

## 4. Tone Generator:

The main propose of Tone Generator block is take two cosine waves from DDS cores and add them in order to produce one wave called tone out.

### 5. Frequency Detector:

Input to the Frequency Detector module is noise bits, which is the output from additive white Gaussian noise.

6. The Output of the block is indices and magnitudes. As per the scope of the project, there are three variants of frequency detector block

- 1. FFT-128 core

- 2. Goertzel algorithm

- 3. Resource sharing

This paper presents about FFT based DTMF Detection.

### III. FFT - 128 CORE

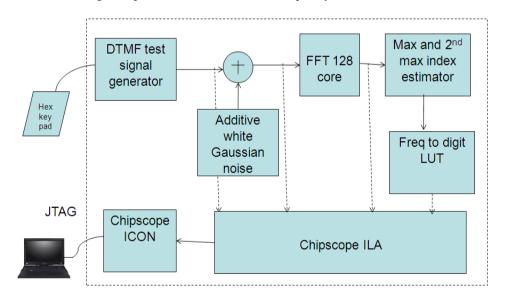

FFT- 128 core: The below figure represents the FFT core as a Frequency detector module.

Fig.3 Block Diagram with FFT-128 Core as Frequency Detection Module

The Xilinx LogiCORE<sup>TM</sup> IP Fast Fourier Transform (FFT) implements the Cooley-Tukey FFT algorithm, a computationally efficient method is for calculating the Discrete Fourier Transform (DFT). A fast Fourier transform (FFT) is an efficient algorithm to compute the discrete Fourier transform (DFT) and it's inverse. There are many distinct FFT algorithms involving a wide range of mathematics, from simple complex-number arithmetic to group theory and number theory.

A DFT decomposes a sequence of values into components of different frequencies. This operation is useful in many fields (see discrete Fourier transform for properties and applications of the transform) but computing it is directly from the definition is often too slow to be practical. An FFT is a way to compute the same result more quickly: computing a DFT of N points in the naive way, using the definition, takes  $O(N^2)$  arithmetical operations, while an FFT can compute the same result in only  $O(N \log N)$  operations.

The difference in speed can be substantial, especially for long data sets where N may be in the thousands or millions in practice, the computation time can be reduced by several orders of magnitude in such cases, and the improvement is roughly proportional to  $N/\log(N)$ . This huge improvement made many DFT-based algorithms practical; FFTs are of great importance to a wide variety of applications, from digital signal processing and solving partial differential equations to algorithms for quick multiplication of large integers.

The most well known FFT algorithms depend upon the factorization of N, but (contrary to popular misconception) there are FFTs with O ( $N \log N$ ) complexity for all N, even for prime N. Many FFT algorithms only depend on the fact that  $e^{-\frac{2\pi i}{N}}$  is an N th primitive root of unity, and thus can be applied to analogous transforms over any finite field, such as number-theoretic transforms.

### IV. SIMULATION RESULTS

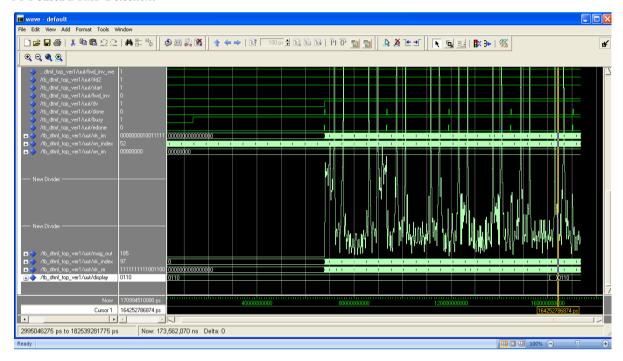

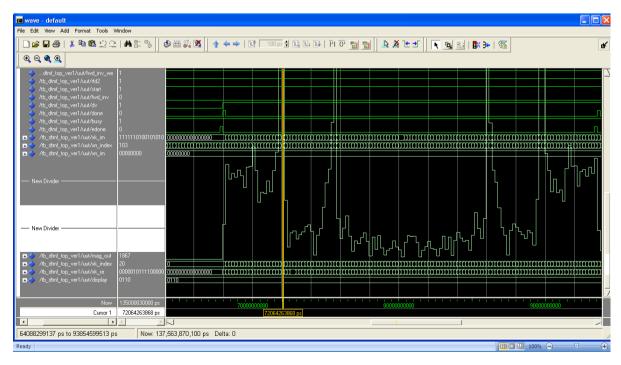

The below figures can represents the simulation results of FFT based DTMF Detection with maximized view by using MODELSIM.

### FFT based DTMF Detection:

Fig. 4 Simulation Results of FFT

Fig. 5 Simulation Results of FFT in Maximized View

### V. SYNTHESIS REPORT

## Synthesis Report for FFT based DTMF Detection:

Device utilization summary: -----

Selected Device: 3s500efg320-4

Number of Slices : 2646 out of 4656 56% Number of Slice Flip Flops : 3256 out of 9312 34% Number of 4 input LUTs : 4268 out of 9312 45%

Number used as logic : 2589 Number used as Shift registers : 431 Number used as RAMs : 1248 Number of IOs : 35

Number of bonded IOBs : 31 out of 232 13% Number of GCLKs : 2 out of 24 8%

Timing Summary: Speed Grade: -5

Minimum period : 17.669ns (Maximum Frequency: 56.596MHz)

Minimum input arrival time before clock : 7.265ns Maximum output required time after clock : 18.417ns Maximum combinational path delay : No path found

### VI. CONCLUSION

This paper presents about the FFT based DTMF detection by using Spartan 3e FPGA because of FPGA technology is increasing its applications in communication technologies. The area, timing and power results are analyzed. For this design the Speed Grade Minimum period is 17.669ns (Maximum Frequency: 56.596MHz), Minimum input arrival time before clock is 7.265ns, Maximum output required time after clock is 18.417ns. In future this paper will extend to Goertzel Algorithm based DTMF detection by Using Resource Sharing Approach on High Speed FPGSs like Virtex SP6 & Zynq 7000 series FPGA family.

#### VI. REFERENCES

- M. D. Felder, J. C. Mason, and B. L. Evans, "Efficient dual-tone Multifrequency detection using the non-uniform discrete [1] Fourier transform," IEEE Signal Process. Lett., vol. 5, no. 7, pp. 160-163, Jul. 1998.

- [2] G. Arslan, B. L. Evans, F. A. Sakarya, and J. L. Pino, \Performance evaluation and real-time implementation of subspace, adaptive, and DFT algorithms for multi-tone detection," in Proc. IEEE Int. Conf. Telecommunications, (Istanbul, Turkey), pp. 884{887, Apr. 1996.

- D. Vanzquez, M. J. Avedillo, G. Huertas, J. M. Quintana, M. Pauritsh, A. Rueda, and J. L. Huertas, "A low-voltage low-power [3] high performance fully integrated DTMF detector," in Proc. IEEE Int. Solid-State Circuits Conf., Sep. 2001, pp. 353-356.

- [4] Zhang Xinyi "The FPGA Implementation of Modified Goertzel Algorithm for DTMF Signal Detection" IEEE 2010, pp.4811-

- J. Nagi\*, K. S. Yap, S. K. Tiong at al. "Intelligent Detection of DTMF Tones using a Hybrid Signal Processing Technique with [5] Support Vector Machines", IEEE 2008.

- [6] Thierry Capitaine, Valery Bourny at. al "Signal processing algorithm on a low resource processor: DTMF strings identification on a DIL8 package microcontroller" IEEE 2008, pp.1050-1054.

- J. Nagi, S. K. Tiong, "Dual-tone Multifrequency Signal Detection using Support Vector Machines" IEEE 2008, pp.350-355.

- [8]

- Li-Te Shen and Shaw-Hwa Hwang" A New Algorithm For Dtmf Detection" IEEE 2009, pp.350-355.

Ge Jinzhao, Zhang Lulin, Qian Yumei, "A new signal detection method based on Goertzel algorithm", Communication [9] Technology, volume 9, pp16-18, 2002;

- [10] Felder D, Mason C, "Efficient Dual-Tone Multi-frequency Detection Using the Nonuniform Discrete Fourier Transform", IEEE Signal Processing Letters, 5(7): pp160-163, 1998;

- [11] Mehran Yahyavi, Arian Ghajarzadeh at al. "An Improvement of MIPS Rate in Detection of DTMF Signals of 64 Subscribers Using GOERTZEL's Algorithm" IEEE 2011, pp.132-136.

- J. A. R. Macias and A. G. Exposito, Feb1998, "Efficient Moving- Window DFT Algorithms," IEEE Trans. Circuits and Systems [12] II: Analog and Digital Signal Processing, vol. 45, no. 2, pp.256-260

- [13] Dr. Rosula S.J. Reyes, Carlos M. Oppus, Jose Claro N. Monje, Noel S. Patron, Reynaldo C. Guerrero, Jovilyn Therese B. Fajardo "FPGA Implementation of a Telecommunications Trainer System" International Journals of Circuits, Systems and Signal processing, PP- 1-9

- [14] S.K.Chaudhari, H.T.Ingale, Rane K.P. Novel Approach of Hybrid Switching System using Combined SPC and VLSI technology, International Journal of Recent Trends in Engineering, Vol 2, No. 5, November 2009, pp.1-9

- [15] Dr. Rosula S.J. Reyes, Carlos M. Oppus, Jose Claro N. Monje, Noel S. Patron, Reynaldo C. Guerrero, Jovilyn Therese B. Fajardo: telecommunications, FPGA Implementation of aTelecommunications Trainer System, pp1-2.

- [16] Adrian E. Conway, Member, and IEEE, A Perspective on the Analytical Performance Evaluation of Multilayered Communication Protocol Architectures, IEEE JOURNAL ON SELFCTED ARFAS IN COMMUNICATIONS, Vol. Y. NO LJANUARY 1991, pp 1-7

- Jason Cong, Yuhui Huang, and Bo Yuan Computer Science Department University of California, Los Angeles Los Angeles, USA, "A Tree-Based Topology Synthesis for On-Chip Network" 978-1-4577-1400-9/11/\$26.00 ©2011 IEEE, pp 2-6

- [18] Naveen Chaudhary, Bursty Communication Performance Analysis of Network-on-Chip with Diverse Traffic Permutations International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-1, Issue-6, January 2012, pp.1-6

- [19] W. J. Dally, B. Towles, Route packets not wires: on-chip interconnection networks, in: Proceedings of Design Automation Conference (DAC'01), ACM, IEEE Press, New York, June 2001, pp. 648–689.

- [20] Xin Wang and Jari Nurmi, Comparison of a Ring On-Chip Network and a Code-Division Multiple-Access On-Chip Network, Hindawi Publishing Corporation VLSI Design Volume2007, ArticleID 18372, 14 pages

- [21] Thiagrajan Viswanathan, "Telecommunication switching system and Networks", 35th Reprinting August 2011, PHI Publishing pp.183-215.

- [22] K.P.Rane, S.V.Patil and A.M.Patil, Efficient combination of Electronics Switching System and VLSI technology, Proceedings of SPIT-IEEE Colloquium and International Conference, Mumbai, India, Vol 2219, pp.1-7

- [23] Texas Instruments. "Modified Goertzel algorithm for DTMF using the MS320C80", application report spra066. 1996.

- [24] Jaquenod A.G., Villagarcia H.A., De giusti M.R. "efficient tone detection solution using programmable logic devices". Argentina: UNLP.

- [25] Dulik T. "an FPGA implementation of Goertzel algorithm" Springer-Verlag Berlin Heidelberg 1999. M. D. Felder, J. C. Mason, and B. L. Evans, "Efficient Dual-tone Mlultifrequency Detection using the Nonuniform Discrete Fourier Transform", IEEE Signal Processing Letters, Vol. 5, No. 7, July 98, pp. 160-163.

- [26] A. M. Shatnawi, A. Abu-El-Haija, and A. M. Elabdalla, "A Digital Receiver for Dual Tone Mlultifrequency (DTMIF) Signals", in Proc. of the Technology Conference, Ottawa, Canada, May 1997, pp. 997-1002.

- [27] M. Popovi6, "Efficient Decoding of Digital DTMIF and R2 Tone Signalization", Facta Univ. Ser., Elec. Energ., Vol. 16, No. 3, December 2003, pp. 389-399.

- [28] M. K. Ravishankar and K. V. S. Hani, "Performance Analysis of Goertzel's Algorithm based Dual-Tone Mlultifrequency (DTMIF) Detection Schemes", Technical Report, ePrints@iisc (India), August 2004.

- [29] M. Popović, "Efficient Decoding of Digital DTMF and R2 Tone Signalization", Facta Univ. Ser., Elec. Energ., Vol. 16, No. 3, December 2003, pp. 389-399.

- [30] P. Mock, \Add DTMF generation and decoding to DSP-\_p designs," EDN, vol. 30, pp. 205{220, Mar. 1985.

- [31] Digit simulation test tape," Tech. Rep. TR-TSY-000763, Bell Communications Research, July 1987.

- [32] ITU Blue Book, Recommendation Q.24: Multi-Frequency Push-Button Signal Reception. 1989.

- [33] M. D. Felder, J. C. Mason, and B. L. Evans, \E\_cient dual-tone multi-frequency detection using the non-uniform discrete Fourier transform," IEEE Signal Processing Letters, vol. 5, pp. 160{163, July 1998.

- [34] S. Park and D. M. Funderburk, \DTMF detection having sample rate decimation and adaptive tone detection." United States Patent, Feb. 1995. Patent Number: 5,392,348.

- [35] J. G. Proakis and D. G. Manolakis, Digital Signal Processing Principles, Algorithms, and Applications. Englewood Cli\_s, NJ: Prentice Hall, 1995.

- [36] S. Bagchi and S. K. Mitra, An e\_cient algorithm for DTMF decoding using the subband NDFT," in Proc.IEEE Int. Sym. Circ. Sys., pp. 1936{1939, May 1995.

- [37] S. L. Gay, J. Hartung, and G. L. Smith, \Algorithms for multi-channel DTMF detection for the WEDSP32 family," in Proc. IEEE Int. Conf. Acoust. Speech Signal Processing, pp. 1134{1137, May 1989.

- [38] V. Friedman, A zero crossing algorithm for the estimation of the frequency of a single sinusoid in white noise," IEEE Trans. Signal Processing, vol. 42, pp. 1565 { 1569, June 1994.

- [39] Sonal Singhal, Piyush Kuchhal "Network on Chip for DTMF Decoder and TDM Switching in Telecommunication Network with HDL Environment" IEEE 2012, pp.1582-1588. Kamal Shaterian, Hossein gharaee "DTMF detection with Goertzel Algorithm using FPGA, a resource sharing approach" IEEE 2010, pp.196-199.

- [40] Smith, G. L. "Dual-Tone Multi-frequency Receiver Using the WEDSP16 Digital Signal processor". AT&T application note.

- [41] Sun, welson, and neuendorffer "FPGA Pipeline Synthesis Design Exploration Using Module Selection and Resource Sharing" IEEE transactions on computer-aided design of integrated circuits and systems, 2007, IEEE Trans. on Computer Aided Design of integrated Circuits and Systems

- [42] Sun, Hua. "Throughput Constrained and Area optimized Dataflow Synthesis for FPGAs" A dissertation submitted to the faculty of Brigham young university in partial fulfillment of the requirements for the degree of doctor of philosophy. Brigham young university, april 2008

- [43] Oppenheim, Alan v. discrete-time signal processing. 1998. 0-13-754920-2. p633-634.

- Texas Instruments Technical White Paper, Carrier Class, High Density VoP White Paper, Jan. 2001, [Online]. Available: http://focus.ti.com/ lit/wp/spey005/spey005.pdf